ASIC Design Unveiled: A Detailed Guide to Development Services and Industry Practices

The semiconductor industry is constantly evolving, mainly making trends with new applications and electronic devices. One of the keys that has contributed to innovation in the ASIC range is an Application-Specific Integrated Circuit. Essentially, ASICs are chips for a particular application, created and designed to provide high performance, efficiency, and optimised functionality in a wide range of devices from smartphones to quantum cryptography systems.

In this comprehensive case study, we’ll investigate the entire ASIC design process, from concept to implementation, developing services and industry practices. In doing so, we will use some examples of real-world applications and provide you with pertinent projects to work through an interactive, as well as interactive, understanding of how ASICs are changing industries.

What Is ASIC?

ASIC is abbreviated for Application-Specific Integrated Circuit. In other words, it’s an application-specific designed chip, not a general-purpose integrated circuit. They combine high performance along with power efficiency and reduction in cost. ASICs are applied where performance, power efficiency, and cost are well in focus. For instance, in QKD systems, where secrecy in data transfer is a must, the use of custom-designed ASICs can ensure low latency as well as power efficiency through an optimized encryption process.

To learn more about ASIC basics, click here.

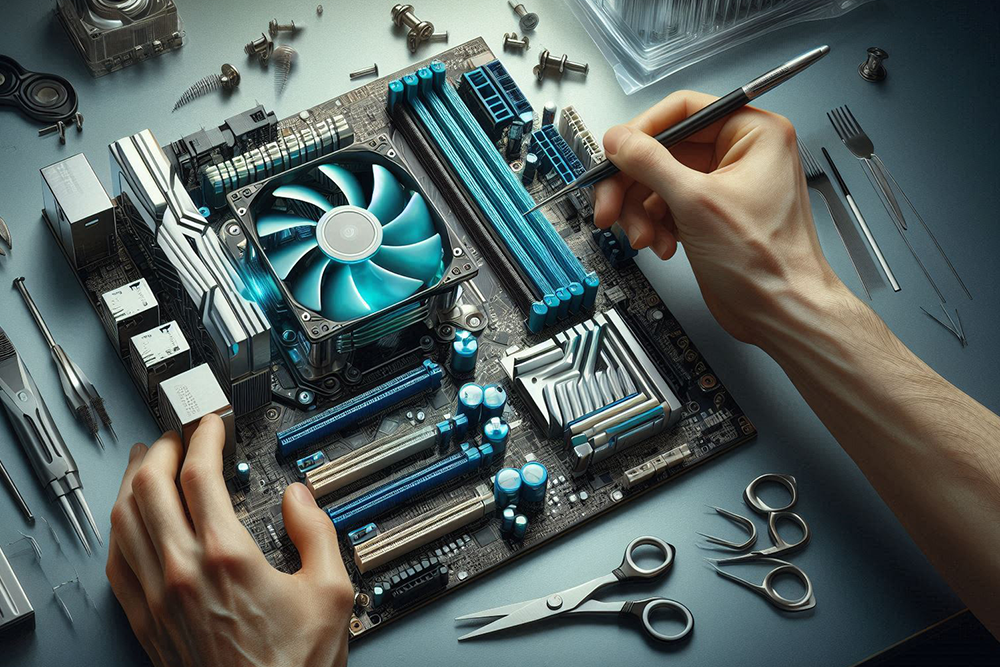

ASIC Design Process

Creating an ASIC is a complex, multi-faceted journey. It has many key stages at which meticulous engineering and numerous cross-functional teams must be involved in the process.

- Specification and Planning: In ASIC development, the first phase is specifying the chip. This means that you have to decide on the functionalities that must be provided by the ASIC. For my project, FPGA-Based Post Processing for QKD, key sifting, error correction, and privacy amplification algorithms are implemented into hardware.

Here, you interact with the stakeholders to ensure that the ASIC shall meet performance targets. That may be in terms of speed, power consumption, or area regarding the physical size of the chip. It usually involves drafting a detailed System Requirement Specification, known as SRS and Architecture Specification Document, or ASD.

- Design, and RTL coding: Once the specifications are defined, it moves to designing the actual architecture of the chip and the writing of the RTL code using such hardware description languages as Verilog or VHDL. The resulting code would essentially be a blueprint of what the ASIC is going to behave like.

Real-life Example: In my practice on Hardware designing of PQC algorithms, we used Verilog to implement post-quantum cryptography algorithms on FPGA, which then became the backbone for ASIC conversion. This experience reflects how code written in RTL is first tested in FPGA before being migrated to ASIC for performance.

To get a better feel about RTL coding, refer here.

- Synthesis and Gate-Level Implementation: After that, the RTL code is verified, and then the netlist of gate-level forms. This stage ensures that the high-level code is being converted into circuit elements that constitute the ASIC-their timing, power, and area constraints.

Real-life Example: In Chiplet Technology Integration for Automotive Applications, synthesis proved to be very crucial in optimizing the consumption and space-related power constraints related to the communication systems that are used inside automobiles.

- Physical Design: During the physical design stage, the gate-level netlist is converted into a physical layout by mapping every logic element onto the silicon wafer. This is achieved by floor planning, placement, routing, and ensuring proper timing and signal integrity. More on physical design – learn how it is important towards achieving your performance goals.

Interactive Tip: Consider this as furnishing your house when you have the blueprint ready. Where you place the sofa, the TV, and the lamps determines the actual appearance and functionality of the room. So is it for an ASIC; its physical layout defines its performance and efficiency.

- Verification and Testing: Design verification must be done with thorough testing and verification before the fabrication of the chip to make sure the design works as specified. Some of the testing methods include functional verification, which tests whether the design works; timing analysis, which checks that data flow occurs appropriately; and power analysis, making sure that power limits are not overstepped by the chip.

Testing is performed using simulation tools emulation platforms, or even FPGA prototypes. In creating test benches that automate verification, tools such as UVM (Universal Verification Methodology) are typically used.

- Fabrication and Packaging: Once all the designs are validated, the chip is shipped to a foundry for manufacturing. The wafer then is diced into individual chips, packaged, and checked out again, and they test it to ensure that it works as anticipated in real-world operating conditions. That’s where the magic happens—your design gets translated into a physical device that might be used inside electronic systems.

Industry Practice in ASIC Design

ASIC development follows many practice keys that are formed by industry standards and real-world requirement. These practices ensure the final product is efficient, scalable, and meets market demands.

- Power Optimization: One of the big requirements in modern ASICs, especially for all battery-operated devices, is power optimization. Techniques like clock gating, voltage scaling, and power gating are meant to be put into place to reduce the consumption of power.

Interactive Insight: In the AI-Powered Infant Cry Classification project, power optimization was an important parameter to ensure that our machine learning model could run on low-power hardware, thereby making it suitable for mobile and wearable devices.

- Time-to-Market Efficiency: One of the greatest challenges when it comes to fast moving industries, like consumer electronics and automotive, is reducing the time it takes to design and deliver an ASIC. To achieve this, companies will employ design automation tools, reuse existing designs called IP cores, and even use parallel development methodologies.

- Security by Design: Security has become a significant concern in ASIC design now with the growth of connected devices within IoT ecosystems. ASICs designed need to be able to withstand attacks. Secure hardware design hence needs to include security features like hardware encryption and designs that resist tampering.

For more on secure hardware design, read here.

Real-Life Examples of ASIC Usage

- Smartphones: The special chips in a smartphone maximize functions like image processing, AI computations, and network connectivity, which make interaction even smoother.

- Automotive Industry: Self-driving cars utilized custom ASICs for sensor data processing, navigation, and safety.

- Cryptography: At PQC, we have custom ASIC designs that allowed faster encryption, less power consumption, thereby safe communication over an untrusted channel.

Problems with ASIC Development

Although high performance and power efficiency, challenges include this:

- High Initial Cost: Only viable for large-scale products, the developing of an ASIC would definitely be of extremely high costs.

- Time to Design: Several months or even years to make a design, since the complexity of the application depends on the complexity of the application.

- Post-fabrication Changes: Errors that are detected after fabrication have the potential of being quite costly and time-consuming, as sometimes the whole chip needs to be re-made.

Conclusion

ASIC design is one of the front-runners of modern electronic innovations. It allows custom solutions for specific applications. Though the process is elaborate and tricky, gains in terms of performance enhancements, power reductions, and optimized functionalities are considerably noteworthy. The future of ASICs will be in domains of quantum computing, AI, and IoT where ASICs will continue driving technological advancement through application-specific designs. Curious for more such case studies? Check out Nano Genius Technologies for more insights!

Frequently Asked Questions

- FPGA vs ASIC:

FPGA is reprogrammable, good for prototyping, whereas ASIC is customized for an application and gives better performance as well as efficiency. For more detailed read case-study ASIC vs FPGA: Case Studies on Prototyping, Design, and Implementation.

- How long will it take to design an ASIC?

ASIC may take anywhere from a few months up to more than a year. It is notorious to vary with complexities and specific requirements of the application.

- Why is it that ASICs can be far more efficient than general-purpose chips? The reason is that ASICs are optimized for only one function. They are small, fast, and power-efficient, where general-purpose chips perform many different functions.