Understanding the ASIC Design Cycle: How It Works

Introduction

Today, electronic devices are changing at a rapid pace and becoming smaller, faster, and more efficient. Behind all these changes lies an important key factor called Application-Specific Integrated Circuits (ASICs).

An ASIC is a custom-designed chip which does a specific function on the device. Unlike general-purpose microprocessors, which may execute any number of things within a computer or smartphone, an ASIC is designed and constructed for one specific task only. The chip inside a digital camera might be optimized for image processing. The chip in a smartwatch can take care of fitness tracking. In summary, the specialized design aids in better performance, consumption of power, and overall saving for the device.

Instead, they are tailored for dedicated tasks with optimized performance, reduced power consumption, and minimized costs. But behind this specialized chip creation lies a complex, iterative process known as the ASIC Design Cycle. The following blog unscrambles the process, emphasizing important concepts, tools, and methodologies.

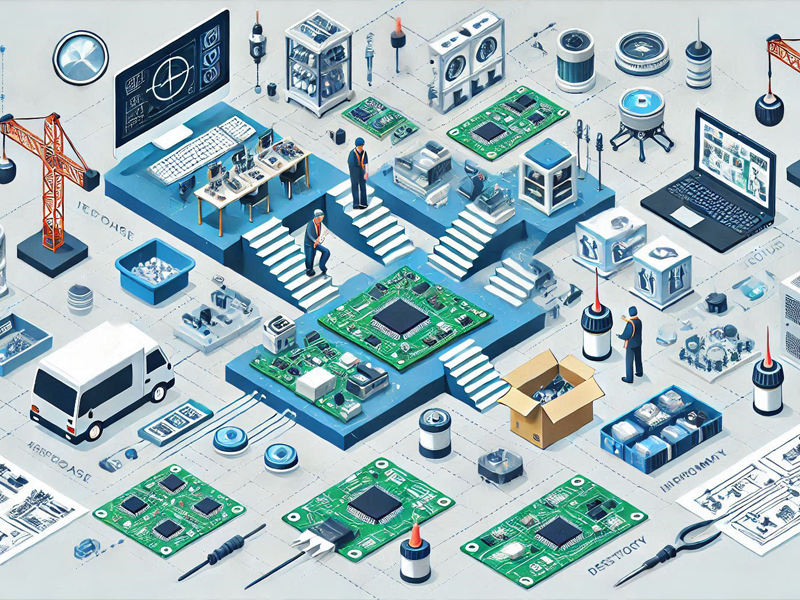

What Is an ASIC Design Cycle?

The ASIC design cycle is the sequence of steps taken to conceptualize, design, verify, manufacture, and test a custom chip. It is a very structured process in which the final chip meets demanding PPA requirements and is free of functional defects.

In general, the design cycle can be divided into the following stages:

- Specification and Planning

- RTL Design

- Functional Verification

- Logic Synthesis

- Physical Design

- Static Timing Analysis (STA)

- Tape-Out

- Fabrication

- Post-Silicon Validation

For insights into real-world ASIC applications, explore this Case Study on ASIC Design Techniques for Multi-Processor System-on-Chip (MPSoC) Development.

1. Specification and Planning

The first step in the ASIC design cycle is to define the functional specifications. This includes:

- Identify the chip’s intended purpose.

- These are key performance metrics-speed, power, and area.

- Define the target process technology e.g., 7nm, 28nm.

- Outlining I/O requirements, power supply, and clock speed.

Marketing teams, architects, and system engineers work together to ensure that the design meets business goals and end-user requirements. Tools like system-level modeling help in the feasibility analysis.

2. RTL Design

At this stage, engineers generate the Register Transfer Level (RTL) code that will explain how a chip is expected to act. Consider the RTL to be an intimate blueprint where data flow among registers and how computational processes take place at any clock cycle can be elaborated upon.

RTL is written in special hardware description languages called Verilog and VHDL. The latter was put into place with specific uses in designing digital circuits.

Key Activities Included:

Architecture Design

Engineers start by sketching high-level block diagrams that describe the significant functions of the chip. Each of these diagrams then forms the basis for RTL modules that define specific tasks and how they are carried out. For instance, the memory controller is translated from a high-level diagram, and the RTL module represents how it works.

Datapath and Control Logic Design:

- Datapath Design: This involves creating hardware components that perform computations, such as Arithmetic Logic Units (ALUs), multiplexers, and registers. The Datapath defines how data flows and gets processed within the chip.

- Control Logic Design: Finite State Machines, how in logic terms, the different items on the chip are used to tell what, under a certain state, is required to be performed on a particular stage.

Tools Applied:

Tools like Synopsys Design Compiler or Cadence Xcelium assist in writing and debugging RTL.

3. Functional Verification

Once the RTL code is written, the most important stage is functional verification. Here, it verifies the functionality of the chip against the specifications. The chip is then tested to see if it functions correctly about its intended functionality before further development in the design stage.

How Verification Works:

Writing Testbenches

The engineers design the test benches, which is the simulation environment in which the chip can be tested. The test benches produce the input signals and forward these to the chip. Then they check whether the result corresponds to what is expected. For example, when testing an ALU, the testbench would forward a few arithmetic problems to test whether it gives the correct solution.

Formal Verification:

In addition, formal verification techniques are used to check the testbenches. Formal verification techniques mathematically prove that the chip design is free of logical errors by checking all possible scenarios, not just the ones tested by simulations.

Tools and Techniques Used:

- UVM: This is a standard framework that assists in sorting out test benches and hence the verification process. It makes the verification process scalable and easier to handle.

- Verification Tools: Industry-standard tools used include Mentor Questa and Cadence JasperGold to simulate, check properties, and catch design bugs in the early stage.

Engineers are supposed to identify and rectify errors at this point which will save a lot of time and costs that are much higher if problems will turn up later on in the course of the process.

4. Logic Synthesis

That completes the logic synthesis: an abstract view, usually called the RTL, will get converted into a more concrete level of netlist. Here, the netlist depicts the detailed version of a chip by employing basic logical gates such as AND and OR gates along with some flip-flops which act more like a blueprint on the silicon as to how different physical components would be linked one to another.

This step plays a critical role in creating cost-effective and efficient chips. To understand how to optimize this step in collaboration with industry experts, read The Advantages of Partnering with Top Semiconductor Distributors.

How It Works:

Synthesis processes take RTL code and map it onto standard cells from a given technology library. Each standard cell is a physical building block, such as a NAND gate, inverter, or memory element, following the target manufacturing technology, such as 7nm or 14nm.

Major Points:

1. Timing, Area, and Power Optimization

- Timing: Satisfying the timing constraints is necessary so that the chip runs at the expected clock speed.

- Chip Area: reducing the physical size to reduce costs.

- Reduced Power: Low power consumption results in increased battery life and lower heat generation.

2. Technology-Specific Design Representation: The output generated should be compatible with the chosen fabrication technology. Indeed, there exist standard cell libraries and process rules for different manufacturers such as TSMC or GlobalFoundries.

Tools Utilized:

Engineers often use synthesis tools such as Synopsys Design Compiler and Cadence Genus. These help in automation because they somehow optimize the design to either maximum speed or minimum power consumption, which then reflects in a better implementation. It is at the stage’s end that the design is ready for the next step, which is known as the physical design: When the netlist transforms into an actual layout for manufacturing.

5. Physical Design

In physical design, the gate-level netlist is mapped to a layout that can be manufactured. This is a multi-stage process and involves:

- Floorplanning: Decide the placement of the large blocks and I/O pads.

- Placement: Optimal arrangement of the standard cells within the floorplan.

- Clock Tree Synthesis (CTS): Synthesis of a balanced clock distribution network.

- Routing: Connection of all components using metal interconnects.

- Design Rule Checking (DRC): Checking whether the layout follows the fabrication constraints.

Much of this process is automated by EDA tools like Cadence Innovus and Synopsys ICC2.

6. Static Timing Analysis (STA)

STA is essential to ensure that the designed chip meets the timing criteria under all possible conditions-temperature, voltage, or manufacturing process variations. Thus, it includes identifying:

- Critical Paths: Those that are the longest data paths under which delays may cause issues with timing.

- Checking Setup and Hold Times: The signals must arrive within the time windows permitted to avoid data corruption.

Tools like Synopsys Primetime and Cadence Tempus run the timing analysis to detect violations and suggest fixes for ensuring that the chip functions properly under all conditions.

7. Tape-out

The term “tape-out” is the last step before fabrication, where the design is sent to the foundry. At this point:

- The layout is checked for correctness using techniques such as Layout vs. Schematic (LVS) and Power Integrity Analysis.

- It is then brought into some photolithographic format, such as GDSII or OASIS.

8. Fabrication

The design is submitted to a semiconductor foundry (TSMC, Samsung, etc.). These companies etch the design onto silicon wafers using advanced lithography techniques. This is a very resource-intensive operation, using

- Wafer preparation.

- Lithography and etching.

- Deposition and doping.

The outcome of this process is a silicon wafer with several copies of the ASIC.

9. Post-Silicon Validation

After fabrication, the chips are tested rigorously in real-world conditions to determine their functionality. This involves:

- Parametric testing: Measurement of electric parameters.

- Functional testing: Does the chip match the design intent?

- Burn-in testing: It stresses the chip to detect early-life failures.

The defective chips are discarded and the good ones are packaged and delivered.

Challenges in the ASIC Design Cycle

ASIC design also remains challenging despite the significant improvement in tools and methodologies.

- High cost: Fabrication and tools are expensive, very especially at advanced nodes like 5nm or 3nm.

- Time-to-market pressures: The pressure of constantly meeting deadlines without sacrificing quality.

- Power and thermal management: As transistors are crammed tightly, heat dissipation becomes a major challenge.

- Verification complexity: As designs grow in size, it’s getting very difficult to verify their correctness.

Future Trends in ASIC Design

ASIC design is in continuous motion owing to technologically advanced approaches. Some of the trends that will define this industry in the future include the following:

- AI-Based Design: This technology is changing ASIC design through AI and ML. It can make complicated tasks such as placement, routing, and error detection automatic and therefore hasten the design cycle. With AI-based algorithms, it becomes possible to explore all options of designs and potentially increase performance with lower time-to-market.

Know more about “How AI is Driving Innovation in EDA Tools and ASIC Chip Design”.

- Chiplets and 3D integration: Instead of designing a single large chip, engineers are moving towards modular design using chiplets– small, functional blocks that are integrated into a single package. 3D integration involves stacking these chiplets vertically, reducing the space while boosting performance and power efficiency. This approach simplifies the complexity of design and provides customized solutions.

- Low-Power Designs: With portable devices, the requirement of low power consumption is inevitable. Techniques like power gating (shutting off parts of the chip not being used) and adaptive voltage scaling (dynamically adjusting voltage levels) are now a norm. These techniques increase the life of the battery and reduce the heat generation in modern chips.

- Super Nodes: This is a move towards smaller geometries such as 3nm or even 2nm technology nodes that will continue to increase performance while reducing power consumption. The push towards miniaturization increases the complexity of the design and forces innovation in both design, fabrication, and verification, hence requiring advanced manufacturing processes and tools. All these breakthroughs are driving the ASIC design of the future toward efficient, powerful, and scalable electronic devices.

For more on the skills and expertise required for this step, refer to Skills You Need to Build a Career in the Semiconductor Industry.

Conclusion

ASIC design is an interesting mixture of creative engineering and meticulous planning. Every step-from specification to post-silicon validation is critical for the final chip to meet the goals of performance, power, and area. Challenges are certainly present, but improvements in EDA tools, fabrication technology, and design methodologies are continually raising the bar on what ASICs can accomplish.

This cycle explains much of how modern electronic devices come to life, unveiling the huge amount of effort that goes into every chip of custom silicon powering industry innovation in consumer electronics, autos, health care, and beyond. For additional blogs and case studies, we invite vendors to explore our content at Nanogenius Technologies.